100G Bit Error Ratio Tester

Classification:

100G high-speed bit error ratio test system (PSS BERT17442) is a 100G high-speed signal error performance analyzer, supporting any rate within 10G-32G. The device includes 4-channel PPG, 4-channel ED receiver and transmitter signals, which can work simultaneously or independently. The single channel supports up to 32G rate. This series has timing and continuous detection modes. It can self-define various rates and code patterns required for measurement, and can adjust parameters such as polarity and equalization. It's widely used in the optical test scenarios such as R&D production of 100G module, 100G AOC, optical devices and subsystems. It also provides the best solution for automated production testing of high-speed optical transceiver modules.

- Application

- Characteristic

- Specifications

- Download

-

Application

1. SFP+,SFP28,QSFP28 module test

2. AOC & DAC test

3. Test of optical devices and equipment (BOSA, TOSA & ROSA)

4. Test of high-speed integrated electronic circuits, PCBs, electronic module subsystems and systemsFeatures

1. Multi-rate selection: 10G-32G rate points

2. Support rich patterns: PRBS7, PRBS9, PRBS15, PRBS23, PRBS31, User40

3. Continuous detection and timing detection

4. Adjustable polarity equalization

5. Low output eye diagram jitter signal and short rise time

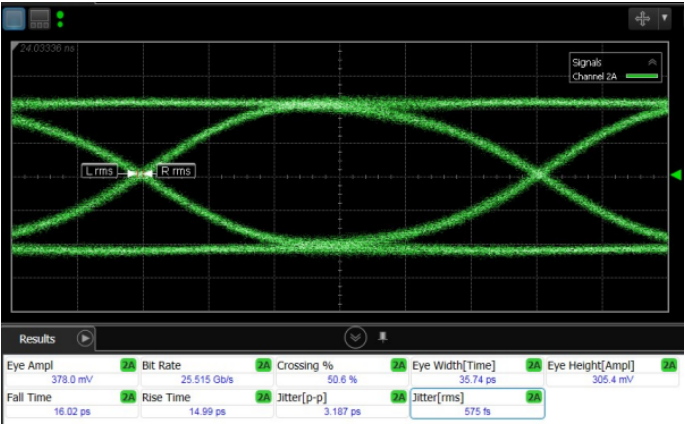

6. Provide secondary development interfaceElectrical eye diagram, test conditions: 25.78G, PRBS31

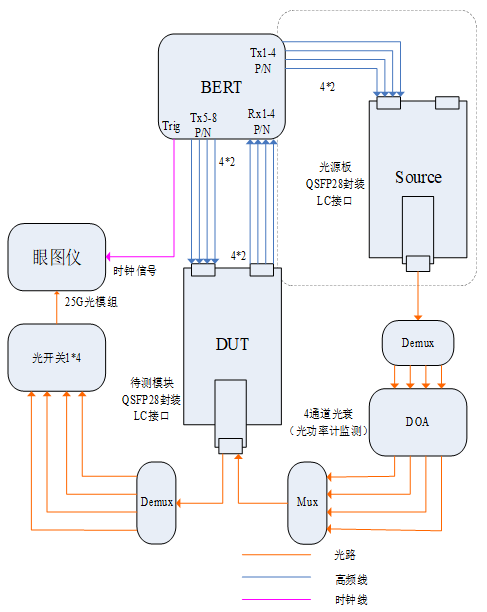

Test Solution

Specification

-

• Multi-rate selection: 10G-32G rate points

• Supports rich code types: PRBS7, PRBS9, PRBS15, PRBS23, PRBS31, User40

• Continuous and timed detection

• Adjustable polarity equalization

• Low jitter and short rise time in the output eye diagram

• Provides secondary development interface

Electrical eye diagram, test conditions: 25.78G, PRBS31

Test plan

-

Parameter

Unit

Typical Value

Rate

Gbps

9.95~15

24.33~32

PPG End

Encoding

PRBS

7、9、11、15、23、31、User pattern 40bit

RMS

fs

1400

700

PP jitter

ps

9.5

4.2

Rise Time (20%~80%)

ps

17

16

Fall Time (20%~80%)

ps

17.5

16.5

Electrical Transmission Channel Amplitude

mv

< 1000

ED End

Encoding

PRBS

7、9、11、15、23、31

Receiving Level Sensitivity

mv

> 40

Input and Output Impedance

Ω

Single-ended 50 Differential 100

Trigger out

Trigger Clock Frequency Ratio

-

1/8 Frequency Division

Ref Clock in

External Clock Input Amplitude

mv

600-1600

Clock Input Percentage

%

40~60

RF Interface

-

K-type 2.92mm, Female

Communication Interface

-

RS232

Power Supply

-

AC 100~240V,50~60Hz,15W

Dimensions

mm

370×306×112mm

Key words:

Focus on us

Tel

086-27-8990 8766